Data Structures | |

| struct | _port_digital_filter_config |

| PORT digital filter feature configuration definition. More... | |

| struct | _port_pin_config |

| PORT pin configuration structure. More... | |

Variables | |

| uint32_t | _port_digital_filter_config::digitalFilterWidth |

| port_digital_filter_clock_source_t | _port_digital_filter_config::clockSource |

| uint16_t | _port_pin_config::pullSelect: 2 |

| uint16_t | : 2 |

| uint16_t | _port_pin_config::slewRate: 1 |

| uint16_t | : 1 |

| uint16_t | : 1 |

| uint16_t | _port_pin_config::passiveFilterEnable: 1 |

| uint16_t | : 1 |

| uint16_t | _port_pin_config::openDrainEnable: 1 |

| uint16_t | : 1 |

| uint16_t | _port_pin_config::driveStrength: 1 |

| uint16_t | : 1 |

| uint16_t | : 1 |

| uint16_t | _port_pin_config::mux: 3 |

| uint16_t | : 4 |

| uint16_t | : 3 |

| uint16_t | : 7 |

| uint16_t uint16_t | _port_pin_config::lockRegister: 1 |

| uint16_t | : 1 |

Configuration | |

| static void | PORT_SetPinConfig (PORT_Type *base, uint32_t pin, const port_pin_config_t *config) |

| Sets the port PCR register. | |

| static void | PORT_SetMultiplePinsConfig (PORT_Type *base, uint32_t mask, const port_pin_config_t *config) |

| Sets the port PCR register for multiple pins. | |

| static void | PORT_SetMultipleInterruptPinsConfig (PORT_Type *base, uint32_t mask, port_interrupt_t config) |

| Sets the port interrupt configuration in PCR register for multiple pins. | |

| static void | PORT_SetPinMux (PORT_Type *base, uint32_t pin, port_mux_t mux) |

| Configures the pin muxing. | |

| static void | PORT_EnablePinsDigitalFilter (PORT_Type *base, uint32_t mask, bool enable) |

| Enables the digital filter in one port, each bit of the 32-bit register represents one pin. | |

| static void | PORT_SetDigitalFilterConfig (PORT_Type *base, const port_digital_filter_config_t *config) |

| Sets the digital filter in one port, each bit of the 32-bit register represents one pin. | |

Interrupt | |

| static void | PORT_SetPinInterruptConfig (PORT_Type *base, uint32_t pin, port_interrupt_t config) |

| Configures the port pin interrupt/DMA request. | |

| static void | PORT_SetPinDriveStrength (PORT_Type *base, uint32_t pin, uint8_t strength) |

| Configures the port pin drive strength. | |

| static uint32_t | PORT_GetPinsInterruptFlags (PORT_Type *base) |

| Reads the whole port status flag. | |

| static void | PORT_ClearPinsInterruptFlags (PORT_Type *base, uint32_t mask) |

| Clears the multiple pin interrupt status flag. | |

Detailed Description

Typedef Documentation

◆ port_digital_filter_clock_source_t

Digital filter clock source selection.

◆ port_digital_filter_config_t

| typedef struct _port_digital_filter_config port_digital_filter_config_t |

PORT digital filter feature configuration definition.

◆ port_interrupt_t

| typedef enum _port_interrupt port_interrupt_t |

Configures the interrupt generation condition.

◆ port_mux_t

| typedef enum _port_mux port_mux_t |

Pin mux selection.

◆ port_pin_config_t

| typedef struct _port_pin_config port_pin_config_t |

PORT pin configuration structure.

Enumeration Type Documentation

◆ _port_digital_filter_clock_source

Digital filter clock source selection.

| Enumerator | |

|---|---|

| kPORT_BusClock | Digital filters are clocked by the bus clock. |

| kPORT_LpoClock | Digital filters are clocked by the 1 kHz LPO clock. |

Definition at line 140 of file fsl_port.h.

◆ _port_drive_strength

| enum _port_drive_strength |

Configures the drive strength.

| Enumerator | |

|---|---|

| kPORT_LowDriveStrength | Low-drive strength is configured. |

| kPORT_HighDriveStrength | High-drive strength is configured. |

Definition at line 72 of file fsl_port.h.

◆ _port_interrupt

| enum _port_interrupt |

Configures the interrupt generation condition.

Definition at line 113 of file fsl_port.h.

◆ _port_lock_register

| enum _port_lock_register |

Unlock/lock the pin control register field[15:0].

| Enumerator | |

|---|---|

| kPORT_UnlockRegister | Pin Control Register fields [15:0] are not locked. |

| kPORT_LockRegister | Pin Control Register fields [15:0] are locked. |

Definition at line 81 of file fsl_port.h.

◆ _port_mux

| enum _port_mux |

Pin mux selection.

Definition at line 90 of file fsl_port.h.

◆ _port_open_drain_enable

Open Drain feature enable/disable.

| Enumerator | |

|---|---|

| kPORT_OpenDrainDisable | Open drain output is disabled. |

| kPORT_OpenDrainEnable | Open drain output is enabled. |

Definition at line 54 of file fsl_port.h.

◆ _port_passive_filter_enable

Passive filter feature enable/disable.

| Enumerator | |

|---|---|

| kPORT_PassiveFilterDisable | Passive input filter is disabled. |

| kPORT_PassiveFilterEnable | Passive input filter is enabled. |

Definition at line 63 of file fsl_port.h.

◆ _port_pull

| enum _port_pull |

Internal resistor pull feature selection.

| Enumerator | |

|---|---|

| kPORT_PullDisable | Internal pull-up/down resistor is disabled. |

| kPORT_PullDown | Internal pull-down resistor is enabled. |

| kPORT_PullUp | Internal pull-up resistor is enabled. |

Definition at line 35 of file fsl_port.h.

◆ _port_slew_rate

| enum _port_slew_rate |

Slew rate selection.

| Enumerator | |

|---|---|

| kPORT_FastSlewRate | Fast slew rate is configured. |

| kPORT_SlowSlewRate | Slow slew rate is configured. |

Definition at line 45 of file fsl_port.h.

Function Documentation

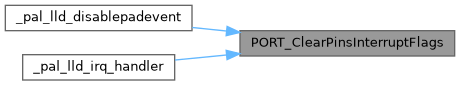

◆ PORT_ClearPinsInterruptFlags()

|

inlinestatic |

Clears the multiple pin interrupt status flag.

- Parameters

-

base PORT peripheral base pointer. mask PORT pin number macro.

Definition at line 462 of file fsl_port.h.

Referenced by _pal_lld_disablepadevent(), and _pal_lld_irq_handler().

◆ PORT_EnablePinsDigitalFilter()

|

inlinestatic |

Enables the digital filter in one port, each bit of the 32-bit register represents one pin.

- Parameters

-

base PORT peripheral base pointer. mask PORT pin number macro.

Definition at line 360 of file fsl_port.h.

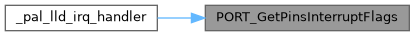

◆ PORT_GetPinsInterruptFlags()

|

inlinestatic |

Reads the whole port status flag.

If a pin is configured to generate the DMA request, the corresponding flag is cleared automatically at the completion of the requested DMA transfer. Otherwise, the flag remains set until a logic one is written to that flag. If configured for a level sensitive interrupt that remains asserted, the flag is set again immediately.

- Parameters

-

base PORT peripheral base pointer.

- Returns

- Current port interrupt status flags, for example, 0x00010001 means the pin 0 and 16 have the interrupt.

Definition at line 451 of file fsl_port.h.

Referenced by _pal_lld_irq_handler().

◆ PORT_SetDigitalFilterConfig()

|

inlinestatic |

Sets the digital filter in one port, each bit of the 32-bit register represents one pin.

- Parameters

-

base PORT peripheral base pointer. config PORT digital filter configuration structure.

Definition at line 378 of file fsl_port.h.

◆ PORT_SetMultipleInterruptPinsConfig()

|

inlinestatic |

Sets the port interrupt configuration in PCR register for multiple pins.

- Parameters

-

base PORT peripheral base pointer. mask PORT pin number macro. config PORT pin interrupt configuration. - kPORT_InterruptOrDMADisabled: Interrupt/DMA request disabled.

- kPORT_DMARisingEdge : DMA request on rising edge(if the DMA requests exit).

- kPORT_DMAFallingEdge: DMA request on falling edge(if the DMA requests exit).

- kPORT_DMAEitherEdge : DMA request on either edge(if the DMA requests exit).

- kPORT_FlagRisingEdge : Flag sets on rising edge(if the Flag states exit).

- kPORT_FlagFallingEdge : Flag sets on falling edge(if the Flag states exit).

- kPORT_FlagEitherEdge : Flag sets on either edge(if the Flag states exit).

- kPORT_InterruptLogicZero : Interrupt when logic zero.

- kPORT_InterruptRisingEdge : Interrupt on rising edge.

- kPORT_InterruptFallingEdge: Interrupt on falling edge.

- kPORT_InterruptEitherEdge : Interrupt on either edge.

- kPORT_InterruptLogicOne : Interrupt when logic one.

- kPORT_ActiveHighTriggerOutputEnable : Enable active high-trigger output (if the trigger states exit).

- kPORT_ActiveLowTriggerOutputEnable : Enable active low-trigger output (if the trigger states exit)..

Definition at line 310 of file fsl_port.h.

◆ PORT_SetMultiplePinsConfig()

|

inlinestatic |

Sets the port PCR register for multiple pins.

This is an example to define input pins or output pins PCR configuration.

- Parameters

-

base PORT peripheral base pointer. mask PORT pin number macro. config PORT PCR register configuration structure.

Definition at line 272 of file fsl_port.h.

◆ PORT_SetPinConfig()

|

inlinestatic |

Sets the port PCR register.

This is an example to define an input pin or output pin PCR configuration.

- Parameters

-

base PORT peripheral base pointer. pin PORT pin number. config PORT PCR register configuration structure.

Definition at line 243 of file fsl_port.h.

◆ PORT_SetPinDriveStrength()

|

inlinestatic |

Configures the port pin drive strength.

- Parameters

-

base PORT peripheral base pointer. pin PORT pin number. config PORT pin drive strength - kPORT_LowDriveStrength = 0U - Low-drive strength is configured.

- kPORT_HighDriveStrength = 1U - High-drive strength is configured.

Definition at line 431 of file fsl_port.h.

Referenced by _pal_lld_setpadmode().

◆ PORT_SetPinInterruptConfig()

|

inlinestatic |

Configures the port pin interrupt/DMA request.

- Parameters

-

base PORT peripheral base pointer. pin PORT pin number. config PORT pin interrupt configuration. - kPORT_InterruptOrDMADisabled: Interrupt/DMA request disabled.

- kPORT_DMARisingEdge : DMA request on rising edge(if the DMA requests exit).

- kPORT_DMAFallingEdge: DMA request on falling edge(if the DMA requests exit).

- kPORT_DMAEitherEdge : DMA request on either edge(if the DMA requests exit).

- kPORT_FlagRisingEdge : Flag sets on rising edge(if the Flag states exit).

- kPORT_FlagFallingEdge : Flag sets on falling edge(if the Flag states exit).

- kPORT_FlagEitherEdge : Flag sets on either edge(if the Flag states exit).

- kPORT_InterruptLogicZero : Interrupt when logic zero.

- kPORT_InterruptRisingEdge : Interrupt on rising edge.

- kPORT_InterruptFallingEdge: Interrupt on falling edge.

- kPORT_InterruptEitherEdge : Interrupt on either edge.

- kPORT_InterruptLogicOne : Interrupt when logic one.

- kPORT_ActiveHighTriggerOutputEnable : Enable active high-trigger output (if the trigger states exit).

- kPORT_ActiveLowTriggerOutputEnable : Enable active low-trigger output (if the trigger states exit).

Definition at line 415 of file fsl_port.h.

Referenced by _pal_lld_disablepadevent(), and _pal_lld_enablepadevent().

◆ PORT_SetPinMux()

|

inlinestatic |

Configures the pin muxing.

- Parameters

-

base PORT peripheral base pointer. pin PORT pin number. mux pin muxing slot selection. - kPORT_PinDisabledOrAnalog: Pin disabled or work in analog function.

- kPORT_MuxAsGpio : Set as GPIO.

- kPORT_MuxAlt2 : chip-specific.

- kPORT_MuxAlt3 : chip-specific.

- kPORT_MuxAlt4 : chip-specific.

- kPORT_MuxAlt5 : chip-specific.

- kPORT_MuxAlt6 : chip-specific.

- kPORT_MuxAlt7 : chip-specific. @Note : This function is NOT recommended to use together with the PORT_SetPinsConfig, because the PORT_SetPinsConfig need to configure the pin mux anyway (Otherwise the pin mux is reset to zero : kPORT_PinDisabledOrAnalog). This function is recommended to use to reset the pin mux

Definition at line 346 of file fsl_port.h.

Variable Documentation

◆ __pad0__

| uint16_t _port_pin_config::__pad0__ |

Definition at line 161 of file fsl_port.h.

◆ __pad10__

| uint16_t _port_pin_config::__pad10__ |

Definition at line 205 of file fsl_port.h.

◆ __pad1__

| uint16_t _port_pin_config::__pad1__ |

Definition at line 167 of file fsl_port.h.

◆ __pad2__

| uint16_t _port_pin_config::__pad2__ |

Definition at line 170 of file fsl_port.h.

◆ __pad3__

| uint16_t _port_pin_config::__pad3__ |

Definition at line 175 of file fsl_port.h.

◆ __pad4__

| uint16_t _port_pin_config::__pad4__ |

Definition at line 181 of file fsl_port.h.

◆ __pad5__

| uint16_t _port_pin_config::__pad5__ |

Definition at line 187 of file fsl_port.h.

◆ __pad6__

| uint16_t _port_pin_config::__pad6__ |

Definition at line 190 of file fsl_port.h.

◆ __pad7__

| uint16_t _port_pin_config::__pad7__ |

Definition at line 194 of file fsl_port.h.

◆ __pad8__

| uint16_t _port_pin_config::__pad8__ |

Definition at line 197 of file fsl_port.h.

◆ __pad9__

| uint16_t _port_pin_config::__pad9__ |

Definition at line 199 of file fsl_port.h.

◆ clockSource

| port_digital_filter_clock_source_t _port_digital_filter_config::clockSource |

Set digital filter clockSource

Definition at line 150 of file fsl_port.h.

◆ digitalFilterWidth

| uint32_t _port_digital_filter_config::digitalFilterWidth |

Set digital filter width

Definition at line 149 of file fsl_port.h.

◆ driveStrength

| uint16_t _port_pin_config::driveStrength |

Fast/slow drive strength configure

Definition at line 185 of file fsl_port.h.

◆ lockRegister

| uint16_t uint16_t _port_pin_config::lockRegister |

Lock/unlock the PCR field[15:0]

Definition at line 203 of file fsl_port.h.

◆ mux

| uint16_t _port_pin_config::mux |

Pin mux Configure

Definition at line 193 of file fsl_port.h.

◆ openDrainEnable

| uint16_t _port_pin_config::openDrainEnable |

Open drain enable/disable

Definition at line 179 of file fsl_port.h.

◆ passiveFilterEnable

| uint16_t _port_pin_config::passiveFilterEnable |

Passive filter enable/disable

Definition at line 173 of file fsl_port.h.

◆ pullSelect

| uint16_t _port_pin_config::pullSelect |

No-pull/pull-down/pull-up select

Definition at line 159 of file fsl_port.h.

◆ slewRate

| uint16_t _port_pin_config::slewRate |

Fast/slow slew rate Configure

Definition at line 165 of file fsl_port.h.