Detailed Description

- Date

- Jan 08, 2022

Definition in file board.c.

Functions | |

| static void | gpio_init (stm32_gpio_t *gpiop, const gpio_setup_t *config) |

| static void | stm32_gpio_init (void) |

| static void | __early_sdram_wait_ready (void) |

| static void | __early_sdram_delay (void) |

| static void | __early_sdram_init (const SDRAMConfig *config) |

| static int | __early_sdram_test (void *base, size_t size) |

| void | __early_init (void) |

| Early initialization code. | |

| bool | sdc_lld_is_card_inserted (SDCDriver *sdcp) |

| SDC card detection. | |

| bool | sdc_lld_is_write_protected (SDCDriver *sdcp) |

| SDC card write protection detection. | |

| bool | mmc_lld_is_card_inserted (MMCDriver *mmcp) |

| MMC_SPI card detection. | |

| bool | mmc_lld_is_write_protected (MMCDriver *mmcp) |

| MMC_SPI card write protection detection. | |

Variables | |

| static const SDRAMConfig | sdram_cfg |

| static const gpio_config_t | gpio_default_config |

| STM32 GPIO static initialization data. | |

Function Documentation

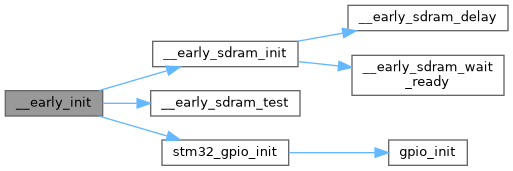

◆ __early_init()

| void __early_init | ( | void | ) |

Early initialization code.

GPIO ports and system clocks are initialized before everything else.

Definition at line 356 of file board.c.

356 {

357

358 stm32_gpio_init();

359 stm32_clock_init();

360

361 /*

362 * Initialise FSMC for SDRAM.

363 */

364#if 0

365 /* clear driver struct */

366 memset(&SDRAMD1, 0 sizeof(SDRAMD1));

367 sdramInit();

368 sdramStart(&SDRAMD1, &sdram_cfg);

369#else

371#endif

372

373 if (0) {

374 /* yes, hardcoded values */

376 }

377}

Here is the call graph for this function:

◆ __early_sdram_delay()

|

static |

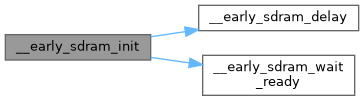

◆ __early_sdram_init()

|

static |

Definition at line 259 of file board.c.

260{

261 uint32_t command_target = 0;

262

263 #ifdef rccResetFSMC

264 rccResetFSMC();

265 #endif

266 rccEnableFSMC(FALSE);

267

268 SDRAM->SDCR1 = config->sdcr;

269 SDRAM->SDTR1 = config->sdtr;

270 SDRAM->SDCR2 = config->sdcr;

271 SDRAM->SDTR2 = config->sdtr;

272

273#if STM32_SDRAM_USE_SDRAM1

274 command_target |= FMC_SDCMR_CTB1;

275#endif

276#if STM32_SDRAM_USE_SDRAM2

277 command_target |= FMC_SDCMR_CTB2;

278#endif

279

280 /* Step 3: Configure a clock configuration enable command.*/

281 __early_sdram_wait_ready();

282 SDRAM->SDCMR = FMCCM_CLK_ENABLED | command_target;

283

284 /* Step 4: Insert delay (tipically 100uS).*/

285 __early_sdram_delay();

286

287 /* Step 5: Configure a PALL (precharge all) command.*/

288 __early_sdram_wait_ready();

289 SDRAM->SDCMR = FMCCM_PALL | command_target;

290

291 /* Step 6.1: Configure a Auto-Refresh command: send the first command.*/

292 __early_sdram_wait_ready();

293 SDRAM->SDCMR = FMCCM_AUTO_REFRESH | command_target |

294 (config->sdcmr & FMC_SDCMR_NRFS);

295

296 /* Step 6.2: Send the second command.*/

297 __early_sdram_wait_ready();

298 SDRAM->SDCMR = FMCCM_AUTO_REFRESH | command_target |

299 (config->sdcmr & FMC_SDCMR_NRFS);

300

301 /* Step 7: Program the external memory mode register.*/

302 __early_sdram_wait_ready();

303 SDRAM->SDCMR = FMCCM_LOAD_MODE | command_target |

304 (config->sdcmr & FMC_SDCMR_MRD);

305

306 /* Step 8: Set clock.*/

307 __early_sdram_wait_ready();

308 SDRAM->SDRTR = config->sdrtr & FMC_SDRTR_COUNT;

309

310 __early_sdram_wait_ready();

311}

Here is the call graph for this function:

◆ __early_sdram_test()

|

static |

Definition at line 313 of file board.c.

314{

315 size_t i;

316 uint32_t *ptr = base;

317

318 /* test 0 */

320 ptr[i] = 0;

321 }

322

324 if (ptr[i] != 0)

325 return -1;

326 }

327

328 /* test 1 */

330 ptr[i] = 0xffffffff;

331 }

332

334 if (ptr[i] != 0xffffffff)

335 return -1;

336 }

337

338 /* test 2 */

340 ptr[i] = i;

341 }

342

344 if (ptr[i] != i)

345 return -1;

346 }

347

348 return 0;

349}

◆ __early_sdram_wait_ready()

|

static |

◆ gpio_init()

|

static |

◆ mmc_lld_is_card_inserted()

| bool mmc_lld_is_card_inserted | ( | MMCDriver * | mmcp | ) |

◆ mmc_lld_is_write_protected()

| bool mmc_lld_is_write_protected | ( | MMCDriver * | mmcp | ) |

◆ sdc_lld_is_card_inserted()

| bool sdc_lld_is_card_inserted | ( | SDCDriver * | sdcp | ) |

◆ sdc_lld_is_write_protected()

| bool sdc_lld_is_write_protected | ( | SDCDriver * | sdcp | ) |

◆ stm32_gpio_init()

|

static |

Definition at line 180 of file board.c.

180 {

181

182 /* Enabling GPIO-related clocks, the mask comes from the

183 registry header file.*/

184 rccResetAHB1(STM32_GPIO_EN_MASK);

185 rccEnableAHB1(STM32_GPIO_EN_MASK, true);

186

187 /* Initializing all the defined GPIO ports.*/

188#if STM32_HAS_GPIOA

190#endif

191#if STM32_HAS_GPIOB

193#endif

194#if STM32_HAS_GPIOC

196#endif

197#if STM32_HAS_GPIOD

199#endif

200#if STM32_HAS_GPIOE

202#endif

203#if STM32_HAS_GPIOF

205#endif

206#if STM32_HAS_GPIOG

208#endif

209#if STM32_HAS_GPIOH

211#endif

212#if STM32_HAS_GPIOI

214#endif

215#if STM32_HAS_GPIOJ

217#endif

218#if STM32_HAS_GPIOK

220#endif

221}

static void gpio_init(stm32_gpio_t *gpiop, const gpio_setup_t *config)

Definition board.c:170

static const gpio_config_t gpio_default_config

STM32 GPIO static initialization data.

Definition board.c:119

Here is the call graph for this function:

Variable Documentation

◆ gpio_default_config

|

static |

STM32 GPIO static initialization data.

Definition at line 118 of file board.c.

118 {

119#if STM32_HAS_GPIOA

120 {VAL_GPIOA_MODER, VAL_GPIOA_OTYPER, VAL_GPIOA_OSPEEDR, VAL_GPIOA_PUPDR,

121 VAL_GPIOA_ODR, VAL_GPIOA_AFRL, VAL_GPIOA_AFRH},

122#endif

123#if STM32_HAS_GPIOB

124 {VAL_GPIOB_MODER, VAL_GPIOB_OTYPER, VAL_GPIOB_OSPEEDR, VAL_GPIOB_PUPDR,

125 VAL_GPIOB_ODR, VAL_GPIOB_AFRL, VAL_GPIOB_AFRH},

126#endif

127#if STM32_HAS_GPIOC

128 {VAL_GPIOC_MODER, VAL_GPIOC_OTYPER, VAL_GPIOC_OSPEEDR, VAL_GPIOC_PUPDR,

129 VAL_GPIOC_ODR, VAL_GPIOC_AFRL, VAL_GPIOC_AFRH},

130#endif

131#if STM32_HAS_GPIOD

132 {VAL_GPIOD_MODER, VAL_GPIOD_OTYPER, VAL_GPIOD_OSPEEDR, VAL_GPIOD_PUPDR,

133 VAL_GPIOD_ODR, VAL_GPIOD_AFRL, VAL_GPIOD_AFRH},

134#endif

135#if STM32_HAS_GPIOE

136 {VAL_GPIOE_MODER, VAL_GPIOE_OTYPER, VAL_GPIOE_OSPEEDR, VAL_GPIOE_PUPDR,

137 VAL_GPIOE_ODR, VAL_GPIOE_AFRL, VAL_GPIOE_AFRH},

138#endif

139#if STM32_HAS_GPIOF

140 {VAL_GPIOF_MODER, VAL_GPIOF_OTYPER, VAL_GPIOF_OSPEEDR, VAL_GPIOF_PUPDR,

141 VAL_GPIOF_ODR, VAL_GPIOF_AFRL, VAL_GPIOF_AFRH},

142#endif

143#if STM32_HAS_GPIOG

144 {VAL_GPIOG_MODER, VAL_GPIOG_OTYPER, VAL_GPIOG_OSPEEDR, VAL_GPIOG_PUPDR,

145 VAL_GPIOG_ODR, VAL_GPIOG_AFRL, VAL_GPIOG_AFRH},

146#endif

147#if STM32_HAS_GPIOH

148 {VAL_GPIOH_MODER, VAL_GPIOH_OTYPER, VAL_GPIOH_OSPEEDR, VAL_GPIOH_PUPDR,

149 VAL_GPIOH_ODR, VAL_GPIOH_AFRL, VAL_GPIOH_AFRH},

150#endif

151#if STM32_HAS_GPIOI

152 {VAL_GPIOI_MODER, VAL_GPIOI_OTYPER, VAL_GPIOI_OSPEEDR, VAL_GPIOI_PUPDR,

153 VAL_GPIOI_ODR, VAL_GPIOI_AFRL, VAL_GPIOI_AFRH},

154#endif

155#if STM32_HAS_GPIOJ

156 {VAL_GPIOJ_MODER, VAL_GPIOJ_OTYPER, VAL_GPIOJ_OSPEEDR, VAL_GPIOJ_PUPDR,

157 VAL_GPIOJ_ODR, VAL_GPIOJ_AFRL, VAL_GPIOJ_AFRH},

158#endif

159#if STM32_HAS_GPIOK

160 {VAL_GPIOK_MODER, VAL_GPIOK_OTYPER, VAL_GPIOK_OSPEEDR, VAL_GPIOK_PUPDR,

161 VAL_GPIOK_ODR, VAL_GPIOK_AFRL, VAL_GPIOK_AFRH}

162#endif

163};

◆ sdram_cfg

|

static |

Initial value:

= {

.sdcr = (uint32_t) (FMC_ColumnBits_Number_8b |

FMC_RowBits_Number_12b |

FMC_SDMemory_Width_16b |

FMC_InternalBank_Number_4 |

FMC_CAS_Latency_3 |

FMC_Write_Protection_Disable |

FMC_SDClock_Period_2 |

FMC_Read_Burst_Disable |

FMC_ReadPipe_Delay_1),

.sdtr = (uint32_t)( (2 - 1) |

(7 << 4) |

(4 << 8) |

(7 << 12) |

(2 << 16) |

(2 << 20) |

(2 << 24)),

.sdcmr = (uint32_t)(((4 - 1) << 5) |

((FMC_SDCMR_MRD_BURST_LENGTH_2 |

FMC_SDCMR_MRD_BURST_TYPE_SEQUENTIAL |

FMC_SDCMR_MRD_CAS_LATENCY_3 |

FMC_SDCMR_MRD_OPERATING_MODE_STANDARD |

FMC_SDCMR_MRD_WRITEBURST_MODE_SINGLE) << 9)),

.sdrtr = (uint32_t)(683 << 1),

}

Definition at line 18 of file board.c.

18 {

19 .sdcr = (uint32_t) (FMC_ColumnBits_Number_8b |

20 FMC_RowBits_Number_12b |

21 FMC_SDMemory_Width_16b |

22 FMC_InternalBank_Number_4 |

23 FMC_CAS_Latency_3 |

24 FMC_Write_Protection_Disable |

25 FMC_SDClock_Period_2 |

26 FMC_Read_Burst_Disable |

27 FMC_ReadPipe_Delay_1),

28

29 .sdtr = (uint32_t)( (2 - 1) | // FMC_LoadToActiveDelay = 2 (TMRD: 2 Clock cycles)

30 (7 << 4) | // FMC_ExitSelfRefreshDelay = 7 (TXSR: min=70ns (7x11.11ns))

31 (4 << 8) | // FMC_SelfRefreshTime = 4 (TRAS: min=42ns (4x11.11ns) max=120k (ns))

32 (7 << 12) | // FMC_RowCycleDelay = 7 (TRC: min=70 (7x11.11ns))

33 (2 << 16) | // FMC_WriteRecoveryTime = 2 (TWR: min=1+ 7ns (1+1x11.11ns))

34 (2 << 20) | // FMC_RPDelay = 2 (TRP: 20ns => 2x11.11ns)

35 (2 << 24)), // FMC_RCDDelay = 2 (TRCD: 20ns => 2x11.11ns)

36

37 .sdcmr = (uint32_t)(((4 - 1) << 5) |

38 ((FMC_SDCMR_MRD_BURST_LENGTH_2 |

39 FMC_SDCMR_MRD_BURST_TYPE_SEQUENTIAL |

40 FMC_SDCMR_MRD_CAS_LATENCY_3 |

41 FMC_SDCMR_MRD_OPERATING_MODE_STANDARD |

42 FMC_SDCMR_MRD_WRITEBURST_MODE_SINGLE) << 9)),

43

44 /* if (STM32_SYSCLK == 180000000) ->

45 64ms / 4096 = 15.625us

46 15.625us * 90MHz = 1406 - 20 = 1386 */

47 //.sdrtr = (1386 << 1),

48 .sdrtr = (uint32_t)(683 << 1),

49};