Detailed Description

This black magic improves hard fault debugging experience

http://www.chibios.com/forum/viewtopic.php?t=2506

Definition in file main_hardfault.c.

Enumerations | |

| enum | FaultType { Reset = 1 , NMI = 2 , HardFault = 3 , MemManage = 4 , BusFault = 5 , UsageFault = 6 } |

Functions | |

| void | NMI_Handler (void) |

| void | logHardFault (uint32_t type, uintptr_t faultAddress, void *sp, struct port_extctx *ctx, uint32_t csfr) |

| void | HardFault_Handler_C (void *sp) |

| void | UsageFault_Handler_C (void *sp) |

| void | MemManage_Handler_C (void *sp) |

Enumeration Type Documentation

◆ FaultType

| enum FaultType |

| Enumerator | |

|---|---|

| Reset | |

| NMI | |

| HardFault | |

| MemManage | |

| BusFault | |

| UsageFault | |

Definition at line 23 of file main_hardfault.c.

Function Documentation

◆ HardFault_Handler_C()

| void HardFault_Handler_C | ( | void * | sp | ) |

Definition at line 34 of file main_hardfault.c.

34 {

35 //Copy to local variables (not pointers) to allow GDB "i loc" to directly show the info

36 //Get thread context. Contains main registers including PC and LR

37 struct port_extctx ctx;

38 memcpy(&ctx, sp, sizeof(struct port_extctx));

39

40 //Interrupt status register: Which interrupt have we encountered, e.g. HardFault?

42 (void)faultType;

43 //For HardFault/BusFault this is the address that was accessed causing the error

44 volatile uint32_t faultAddress = SCB->BFAR;

45

46 //Flags about hardfault / busfault

47 //See http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.dui0552a/Cihdjcfc.html for reference

48 volatile bool isFaultPrecise = ((SCB->CFSR >> SCB_CFSR_BUSFAULTSR_Pos) & (1 << 1) ? true : false);

49 volatile bool isFaultImprecise = ((SCB->CFSR >> SCB_CFSR_BUSFAULTSR_Pos) & (1 << 2) ? true : false);

50 volatile bool isFaultOnUnstacking = ((SCB->CFSR >> SCB_CFSR_BUSFAULTSR_Pos) & (1 << 3) ? true : false);

51 volatile bool isFaultOnStacking = ((SCB->CFSR >> SCB_CFSR_BUSFAULTSR_Pos) & (1 << 4) ? true : false);

52 volatile bool isFaultAddressValid = ((SCB->CFSR >> SCB_CFSR_BUSFAULTSR_Pos) & (1 << 7) ? true : false);

53 (void)isFaultPrecise;

54 (void)isFaultImprecise;

55 (void)isFaultOnUnstacking;

56 (void)isFaultOnStacking;

57 (void)isFaultAddressValid;

58

59 logHardFault(faultType, faultAddress, sp, &ctx, SCB->CFSR >> SCB_CFSR_BUSFAULTSR_Pos);

60

61 // check if debugger is connected

62 if (CoreDebug->DHCSR & CoreDebug_DHCSR_C_DEBUGEN_Msk)

63 {

64 bkpt();

65 }

66 NVIC_SystemReset();

67}

void logHardFault(uint32_t type, uintptr_t faultAddress, void *sp, struct port_extctx *ctx, uint32_t csfr)

Definition bootloader_stubs.cpp:16

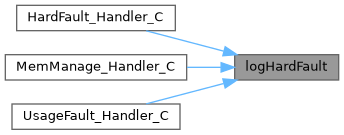

Here is the call graph for this function:

◆ logHardFault()

| void logHardFault | ( | uint32_t | type, |

| uintptr_t | faultAddress, | ||

| void * | sp, | ||

| struct port_extctx * | ctx, | ||

| uint32_t | csfr | ||

| ) |

Definition at line 16 of file bootloader_stubs.cpp.

16{ }

Referenced by HardFault_Handler_C(), MemManage_Handler_C(), and UsageFault_Handler_C().

Here is the call graph for this function:

Here is the caller graph for this function:

◆ MemManage_Handler_C()

| void MemManage_Handler_C | ( | void * | sp | ) |

Definition at line 103 of file main_hardfault.c.

103 {

104 //Copy to local variables (not pointers) to allow GDB "i loc" to directly show the info

105 //Get thread context. Contains main registers including PC and LR

106 struct port_extctx ctx;

107 memcpy(&ctx, sp, sizeof(struct port_extctx));

108

109 //Interrupt status register: Which interrupt have we encountered, e.g. HardFault?

111 (void)faultType;

112 //For HardFault/BusFault this is the address that was accessed causing the error

113 volatile uint32_t faultAddress = SCB->MMFAR;

114

115 //Flags about hardfault / busfault

116 //See http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.dui0552a/Cihdjcfc.html for reference

117 volatile bool isInstructionAccessViolation = ((SCB->CFSR >> SCB_CFSR_MEMFAULTSR_Pos) & (1 << 0) ? true : false);

118 volatile bool isDataAccessViolation = ((SCB->CFSR >> SCB_CFSR_MEMFAULTSR_Pos) & (1 << 1) ? true : false);

119 volatile bool isExceptionUnstackingFault = ((SCB->CFSR >> SCB_CFSR_MEMFAULTSR_Pos) & (1 << 3) ? true : false);

120 volatile bool isExceptionStackingFault = ((SCB->CFSR >> SCB_CFSR_MEMFAULTSR_Pos) & (1 << 4) ? true : false);

121 volatile bool isFaultAddressValid = ((SCB->CFSR >> SCB_CFSR_MEMFAULTSR_Pos) & (1 << 7) ? true : false);

122 (void)isInstructionAccessViolation;

123 (void)isDataAccessViolation;

124 (void)isExceptionUnstackingFault;

125 (void)isExceptionStackingFault;

126 (void)isFaultAddressValid;

127

128 logHardFault(faultType, faultAddress, sp, &ctx, SCB->CFSR);

129

130 // check if debugger is connected

131 if (CoreDebug->DHCSR & CoreDebug_DHCSR_C_DEBUGEN_Msk)

132 {

133 bkpt();

134 }

135 NVIC_SystemReset();

136}

Here is the call graph for this function:

◆ NMI_Handler()

| void NMI_Handler | ( | void | ) |

Definition at line 18 of file main_hardfault.c.

18 {

19 NVIC_SystemReset();

20}

◆ UsageFault_Handler_C()

| void UsageFault_Handler_C | ( | void * | sp | ) |

Definition at line 69 of file main_hardfault.c.

69 {

70 //Copy to local variables (not pointers) to allow GDB "i loc" to directly show the info

71 //Get thread context. Contains main registers including PC and LR

72 struct port_extctx ctx;

73 memcpy(&ctx, sp, sizeof(struct port_extctx));

74

75 //Interrupt status register: Which interrupt have we encountered, e.g. HardFault?

77 (void)faultType;

78 //Flags about hardfault / busfault

79 //See http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.dui0552a/Cihdjcfc.html for reference

80 volatile bool isUndefinedInstructionFault = ((SCB->CFSR >> SCB_CFSR_USGFAULTSR_Pos) & (1 << 0) ? true : false);

81 volatile bool isEPSRUsageFault = ((SCB->CFSR >> SCB_CFSR_USGFAULTSR_Pos) & (1 << 1) ? true : false);

82 volatile bool isInvalidPCFault = ((SCB->CFSR >> SCB_CFSR_USGFAULTSR_Pos) & (1 << 2) ? true : false);

83 volatile bool isNoCoprocessorFault = ((SCB->CFSR >> SCB_CFSR_USGFAULTSR_Pos) & (1 << 3) ? true : false);

84 volatile bool isUnalignedAccessFault = ((SCB->CFSR >> SCB_CFSR_USGFAULTSR_Pos) & (1 << 8) ? true : false);

85 volatile bool isDivideByZeroFault = ((SCB->CFSR >> SCB_CFSR_USGFAULTSR_Pos) & (1 << 9) ? true : false);

86 (void)isUndefinedInstructionFault;

87 (void)isEPSRUsageFault;

88 (void)isInvalidPCFault;

89 (void)isNoCoprocessorFault;

90 (void)isUnalignedAccessFault;

91 (void)isDivideByZeroFault;

92

93 logHardFault(faultType, 0, sp, &ctx, SCB->CFSR);

94

95 // check if debugger is connected

96 if (CoreDebug->DHCSR & CoreDebug_DHCSR_C_DEBUGEN_Msk)

97 {

98 bkpt();

99 }

100 NVIC_SystemReset();

101}

Here is the call graph for this function: