Functions | |

| static NO_CACHE uint8_t tmpbuf[256] | __attribute__ ((aligned(32))) |

| static flash_error_t | jedec_poll_status (SNORDriver *devp) |

| static void | jedec_reset_memory (SNORDriver *devp) |

| static void | jedec_set_config (SNORDriver *devp, uint8_t val) |

| static uint8_t | jedec_get_config (SNORDriver *devp) |

| static void | jedec_write_enable (SNORDriver *devp, int enable) |

| static void | snor_device_fill_cmd (wspi_command_t *cmd, uint32_t cfg, uint8_t opcode, uint8_t mode_clocks, uint8_t dummy_clocks) |

| void | snor_device_init (SNORDriver *devp) |

| flash_error_t | snor_device_read (SNORDriver *devp, flash_offset_t offset, size_t n, uint8_t *rp) |

| flash_error_t | snor_device_program (SNORDriver *devp, flash_offset_t offset, size_t n, const uint8_t *pp) |

| flash_error_t | snor_device_start_erase_all (SNORDriver *devp) |

| flash_error_t | snor_device_start_erase_sector (SNORDriver *devp, flash_sector_t sector) |

| flash_error_t | snor_device_verify_erase (SNORDriver *devp, flash_sector_t sector) |

| flash_error_t | snor_device_query_erase (SNORDriver *devp, uint32_t *msec) |

| flash_error_t | snor_device_read_sfdp (SNORDriver *devp, flash_offset_t offset, size_t n, uint8_t *rp) |

| void | snor_activate_xip (SNORDriver *devp) |

| void | snor_reset_xip (SNORDriver *devp) |

Variables | |

| flash_descriptor_t | snor_descriptor |

| Flash descriptor. | |

| const wspi_command_t | snor_memmap_read |

| Fast read command for memory mapped mode. | |

| static uint32_t | sfdpbuf [64/4] |

| static wspi_command_t | jedec_cmd_read |

| static wspi_command_t | jedec_cmd_erase |

| static wspi_command_t | jedec_cmd_program |

| flash_descriptor_t | snor_descriptor |

| Flash descriptor. | |

| const wspi_command_t | snor_memmap_read |

| Fast read command for memory mapped mode. | |

Detailed Description

Function Documentation

◆ __attribute__()

|

static |

◆ jedec_get_config()

|

static |

Definition at line 204 of file hal_flash_device.c.

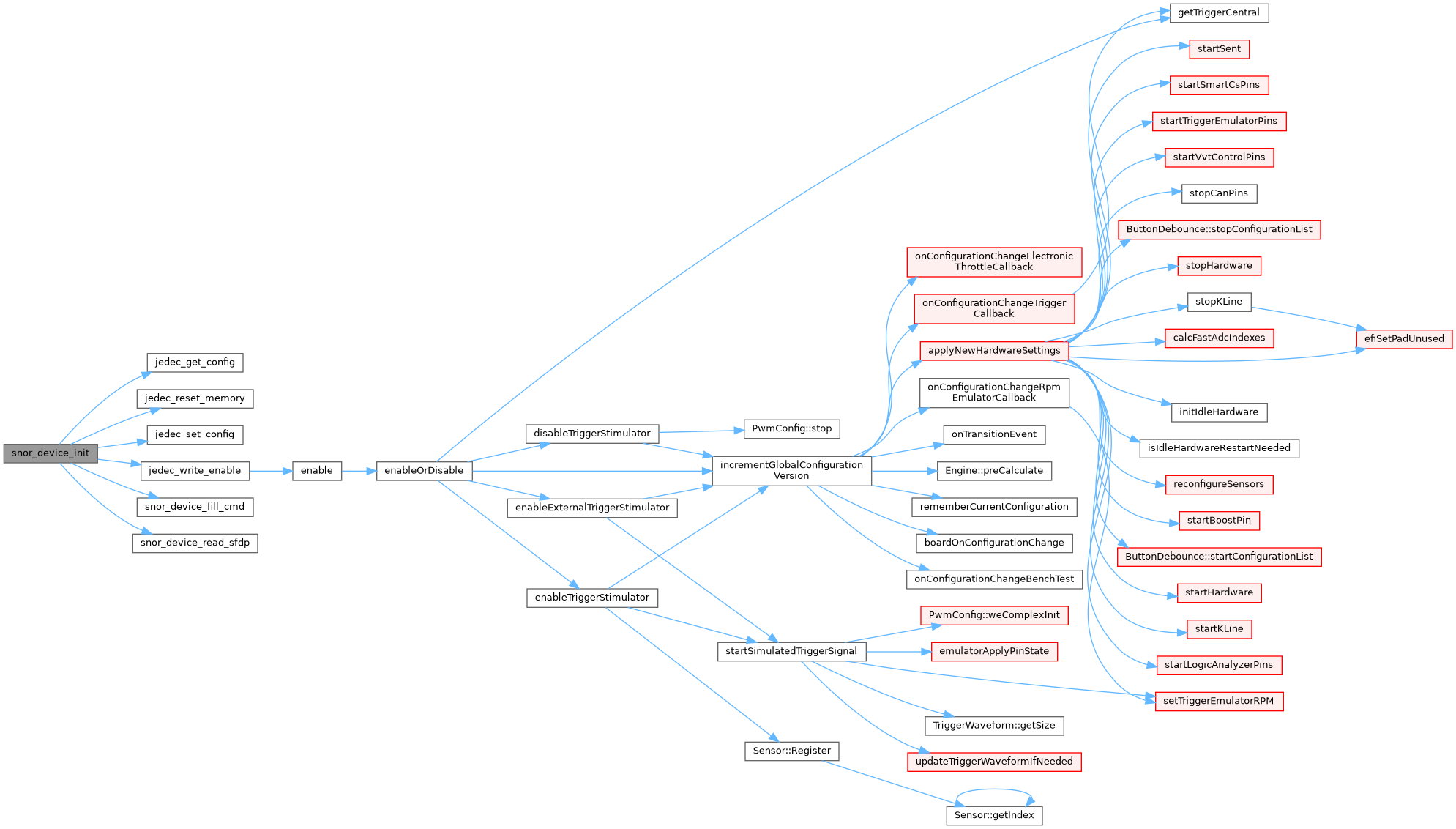

Referenced by snor_device_init().

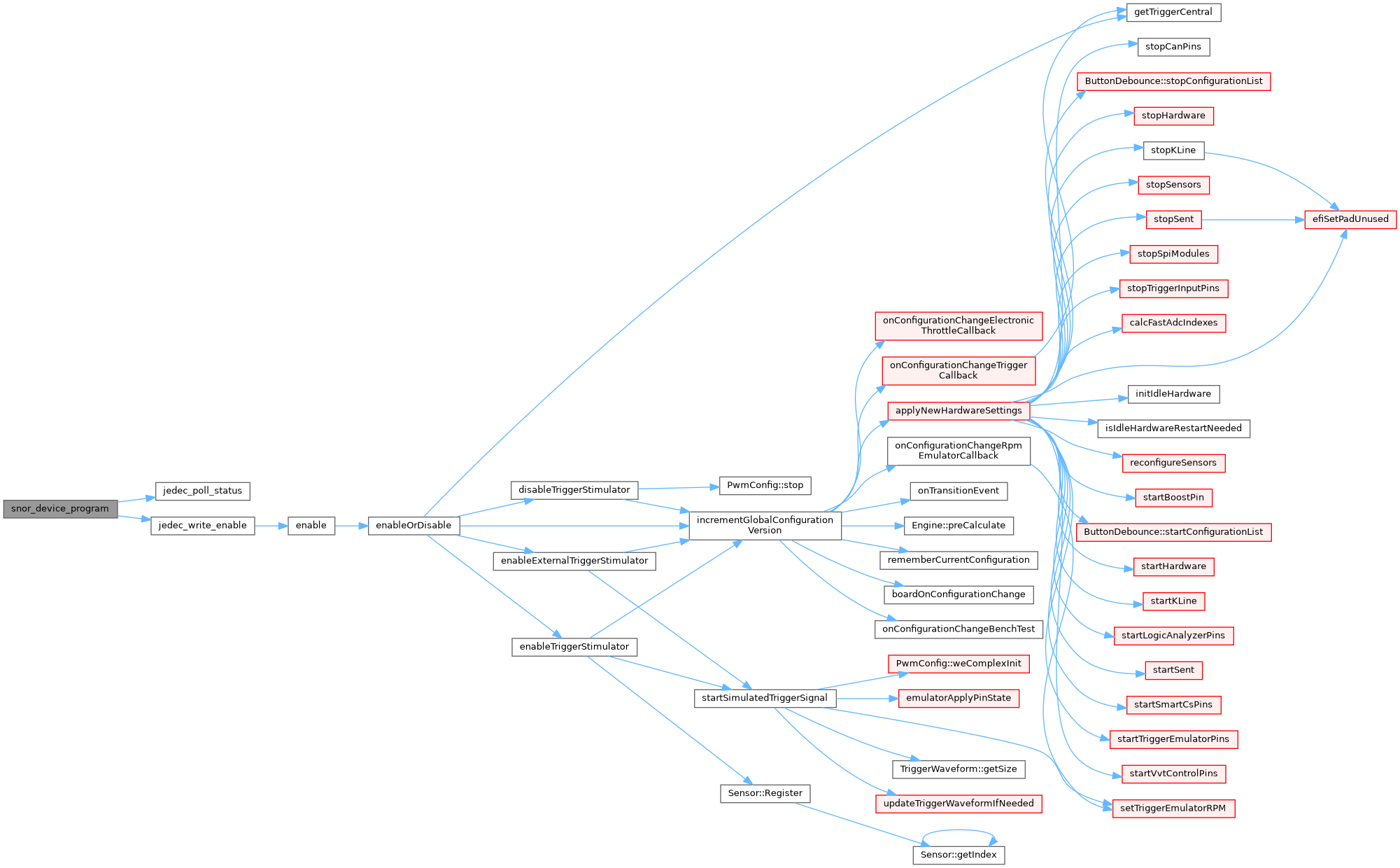

◆ jedec_poll_status()

|

static |

Definition at line 104 of file hal_flash_device.c.

Referenced by snor_device_program().

◆ jedec_reset_memory()

|

static |

Definition at line 121 of file hal_flash_device.c.

Referenced by snor_device_init().

◆ jedec_set_config()

|

static |

Definition at line 196 of file hal_flash_device.c.

Referenced by snor_device_init().

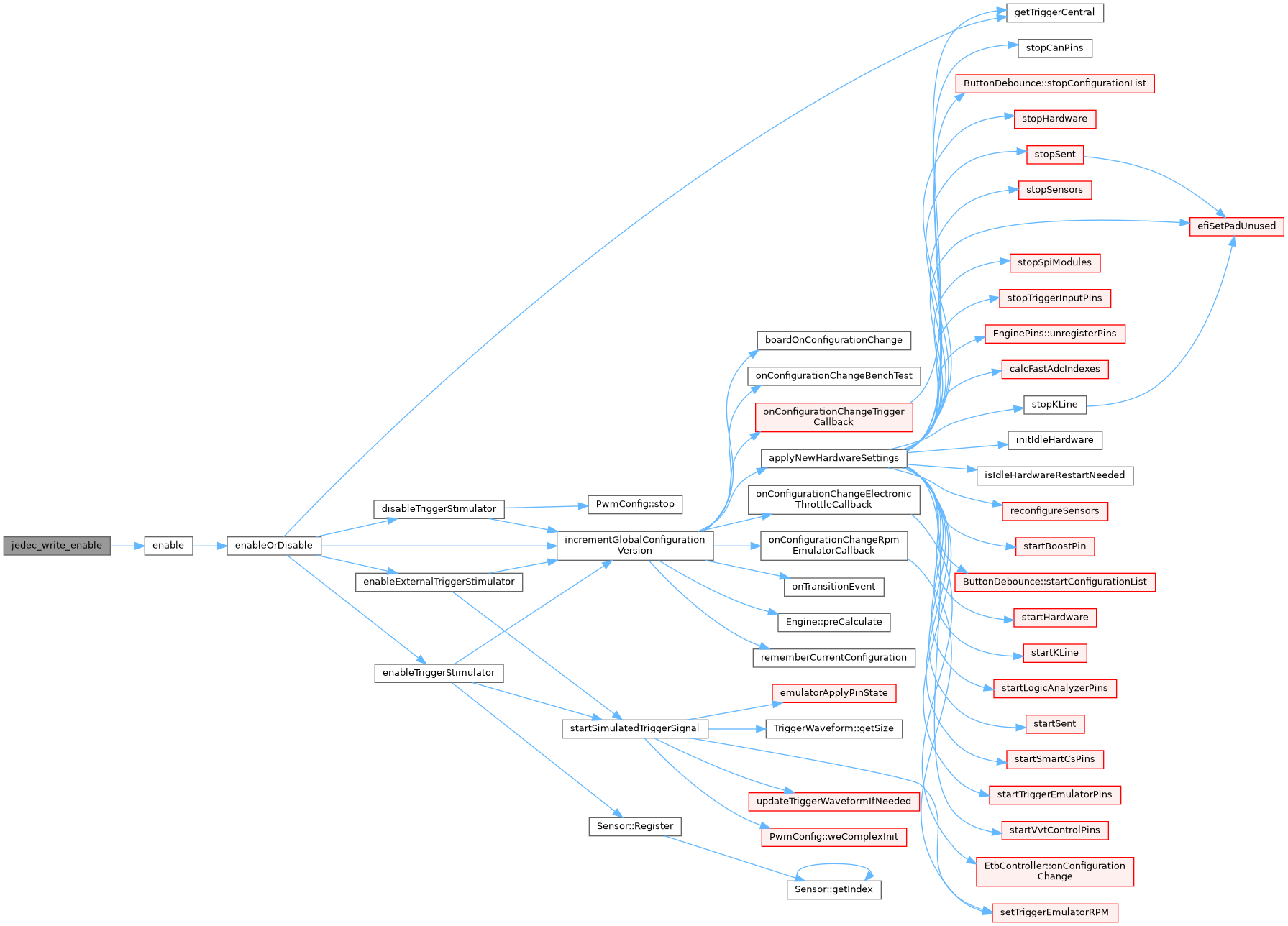

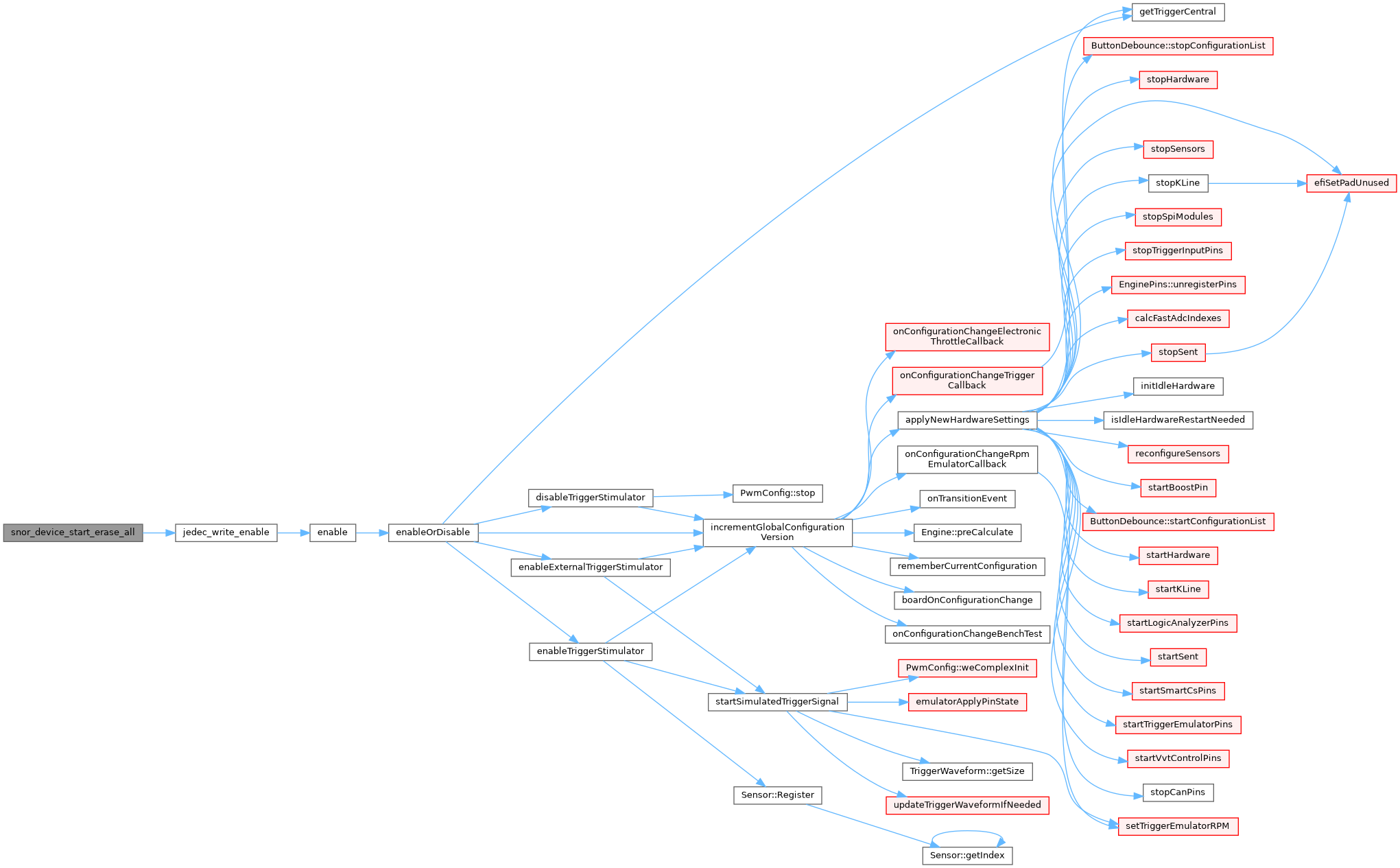

◆ jedec_write_enable()

|

static |

Definition at line 211 of file hal_flash_device.c.

Referenced by snor_activate_xip(), snor_device_init(), snor_device_program(), snor_device_start_erase_all(), snor_device_start_erase_sector(), and snor_reset_xip().

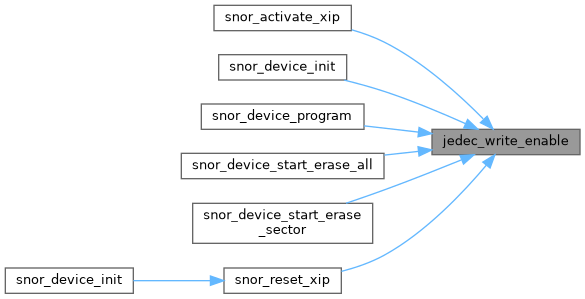

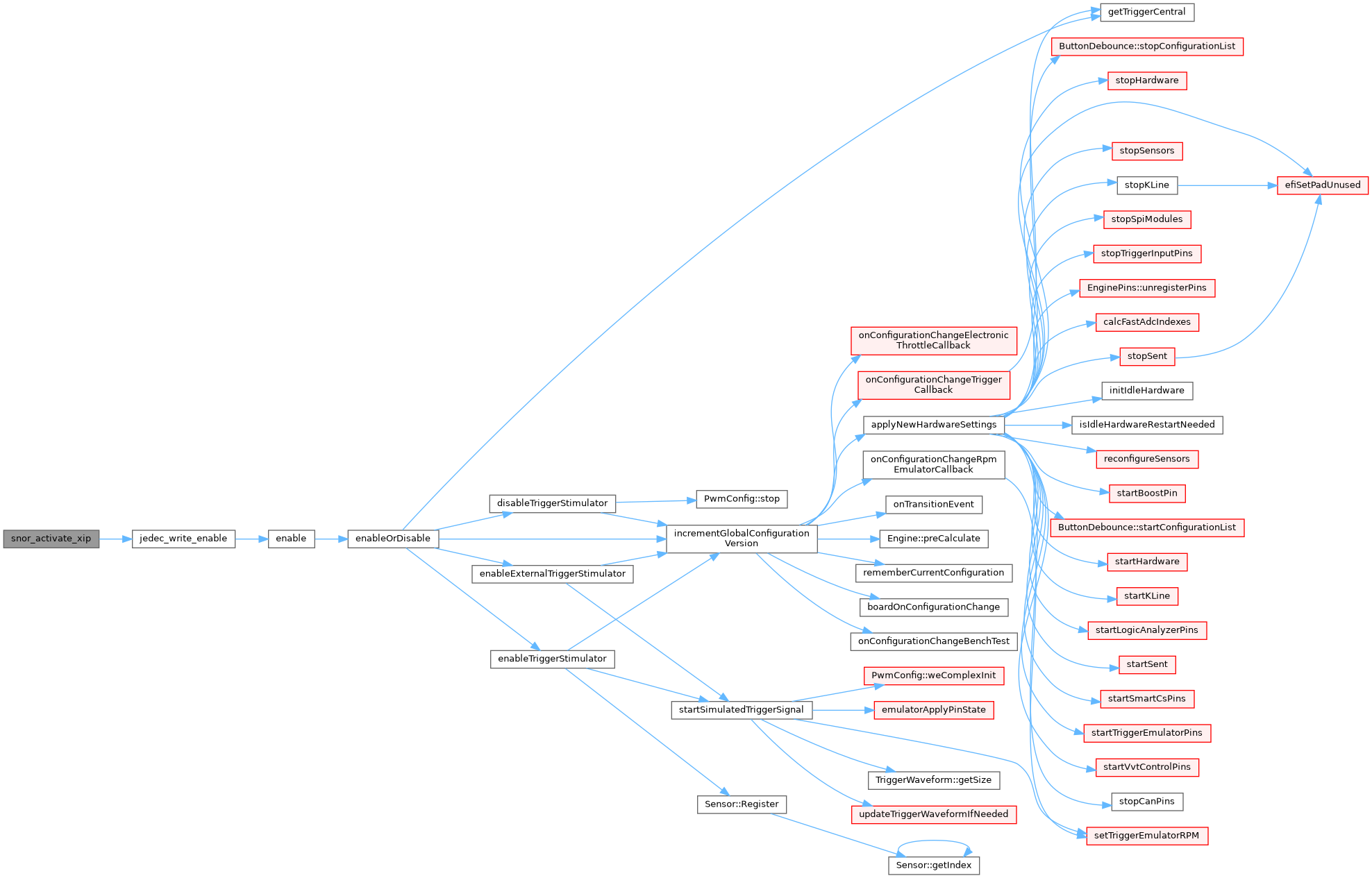

◆ snor_activate_xip()

| void snor_activate_xip | ( | SNORDriver * | devp | ) |

Definition at line 581 of file hal_flash_device.c.

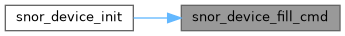

◆ snor_device_fill_cmd()

|

static |

Definition at line 216 of file hal_flash_device.c.

Referenced by snor_device_init().

◆ snor_device_init()

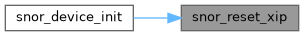

| void snor_device_init | ( | SNORDriver * | devp | ) |

Definition at line 264 of file hal_flash_device.c.

◆ snor_device_program()

| flash_error_t snor_device_program | ( | SNORDriver * | devp, |

| flash_offset_t | offset, | ||

| size_t | n, | ||

| const uint8_t * | pp | ||

| ) |

Definition at line 428 of file hal_flash_device.c.

◆ snor_device_query_erase()

| flash_error_t snor_device_query_erase | ( | SNORDriver * | devp, |

| uint32_t * | msec | ||

| ) |

Definition at line 524 of file hal_flash_device.c.

◆ snor_device_read()

| flash_error_t snor_device_read | ( | SNORDriver * | devp, |

| flash_offset_t | offset, | ||

| size_t | n, | ||

| uint8_t * | rp | ||

| ) |

Definition at line 409 of file hal_flash_device.c.

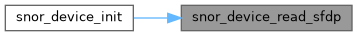

◆ snor_device_read_sfdp()

| flash_error_t snor_device_read_sfdp | ( | SNORDriver * | devp, |

| flash_offset_t | offset, | ||

| size_t | n, | ||

| uint8_t * | rp | ||

| ) |

Definition at line 546 of file hal_flash_device.c.

Referenced by snor_device_init().

◆ snor_device_start_erase_all()

| flash_error_t snor_device_start_erase_all | ( | SNORDriver * | devp | ) |

Definition at line 464 of file hal_flash_device.c.

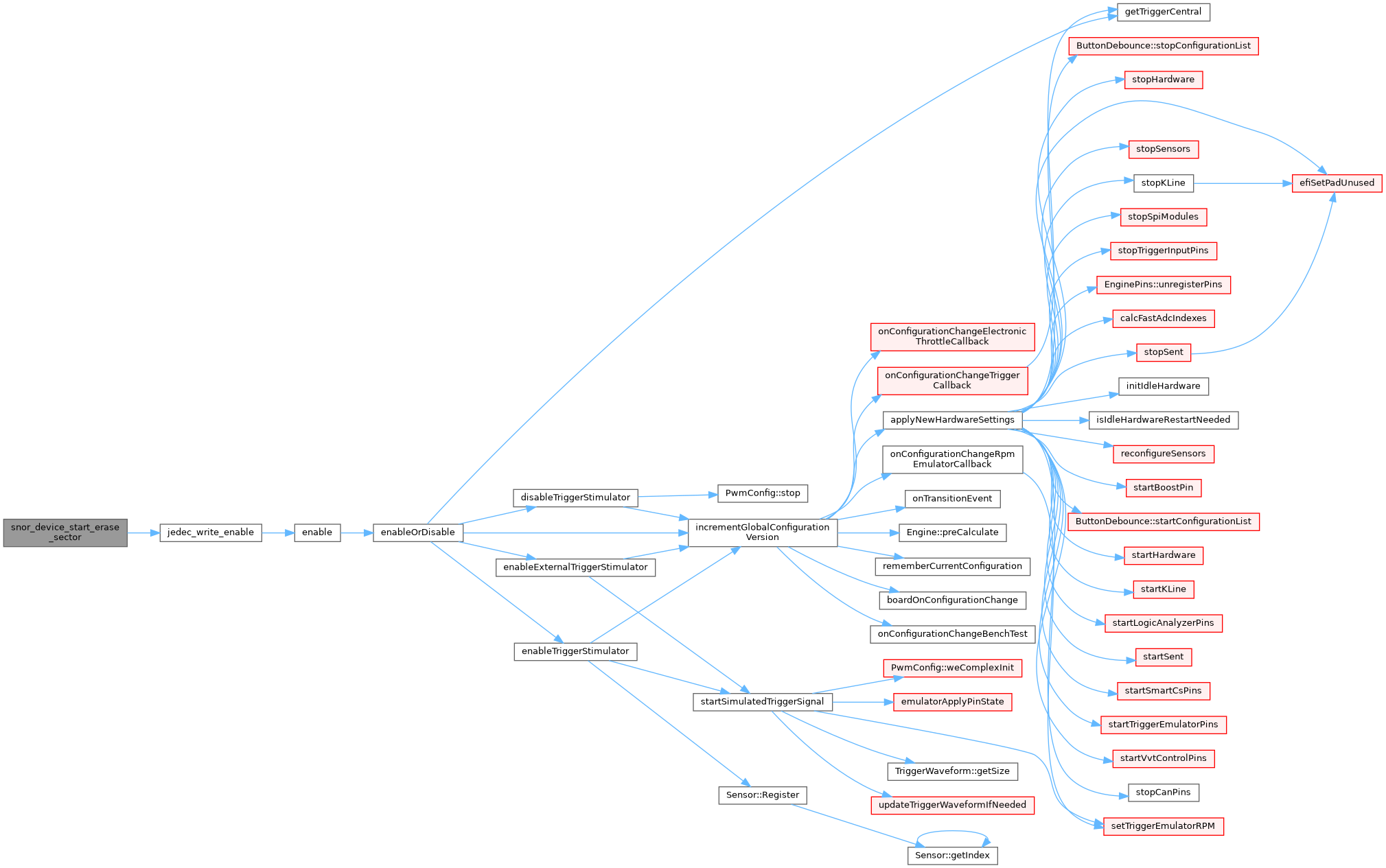

◆ snor_device_start_erase_sector()

| flash_error_t snor_device_start_erase_sector | ( | SNORDriver * | devp, |

| flash_sector_t | sector | ||

| ) |

Definition at line 475 of file hal_flash_device.c.

◆ snor_device_verify_erase()

| flash_error_t snor_device_verify_erase | ( | SNORDriver * | devp, |

| flash_sector_t | sector | ||

| ) |

Definition at line 489 of file hal_flash_device.c.

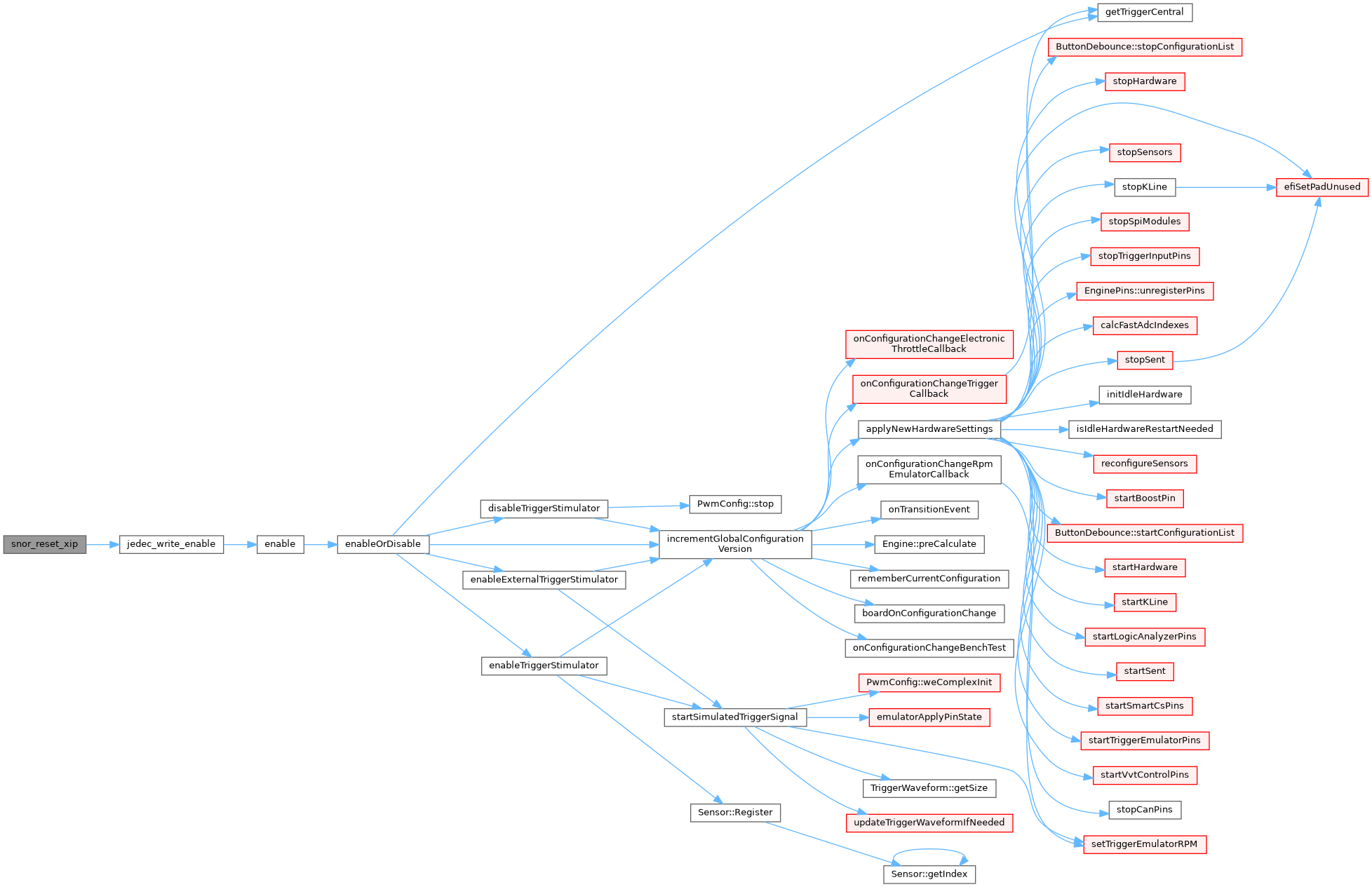

◆ snor_reset_xip()

| void snor_reset_xip | ( | SNORDriver * | devp | ) |

Definition at line 595 of file hal_flash_device.c.

Referenced by snor_device_init().

Variable Documentation

◆ jedec_cmd_erase

|

static |

Definition at line 95 of file hal_flash_device.c.

Referenced by snor_device_init(), and snor_device_start_erase_sector().

◆ jedec_cmd_program

|

static |

Definition at line 98 of file hal_flash_device.c.

Referenced by snor_device_init(), and snor_device_program().

◆ jedec_cmd_read

|

static |

Definition at line 92 of file hal_flash_device.c.

Referenced by snor_device_init(), snor_device_read(), and snor_device_verify_erase().

◆ sfdpbuf

|

static |

Definition at line 89 of file hal_flash_device.c.

Referenced by snor_device_init().

◆ snor_descriptor [1/2]

| flash_descriptor_t snor_descriptor |

Flash descriptor.

Definition at line 39 of file hal_flash_device.c.

Referenced by snor_device_init(), snor_device_program(), snor_device_start_erase_sector(), and snor_device_verify_erase().

◆ snor_descriptor [2/2]

|

extern |

Flash descriptor.

Flash descriptor.

Definition at line 39 of file hal_flash_device.c.

◆ snor_memmap_read [1/2]

| const wspi_command_t snor_memmap_read |

Fast read command for memory mapped mode.

Definition at line 56 of file hal_flash_device.c.

◆ snor_memmap_read [2/2]

|

extern |

Fast read command for memory mapped mode.

Definition at line 56 of file hal_flash_device.c.